SDS Intro & RISC-V Datapath(2): Datapath

RV32I 需要的状态有:

x0-x31的寄存器- 每一个是 32bits, 32 个寄存器

- 由

rs1rs2和rd确定 - 对

x0的写会被忽略

PC- 内存

- 在一个32bits的地址空间里,存有指令和数据

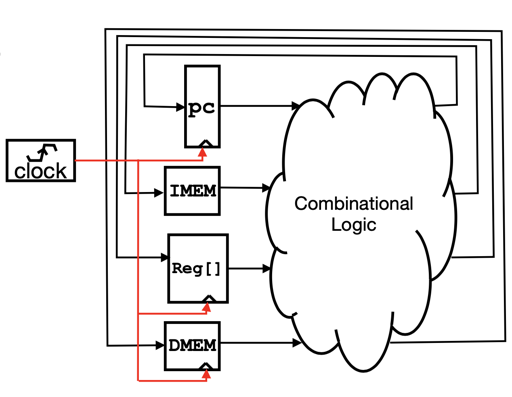

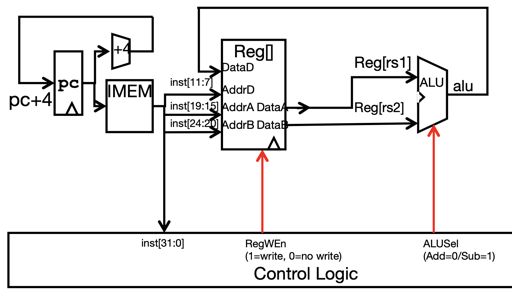

One-Instruction-Per-Cycle RISC-V Machine

- 现有的状态输出和输入走到 combinational logic, 在下个 clock edge 之前设置好下一个状态的值

- clock edge 到来时,所有的状态都会被输出更新,然后执行状态转移到

- 指令和数据的内存是分开的,为了简化,内存是异步读取的,写入是同步的

抽象的逻辑图如下:

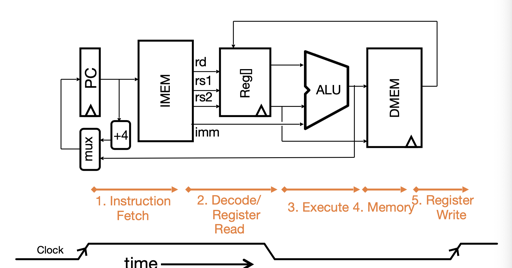

Instruction phase

我们处理一条指令,可以划分为下面这些阶段:

- 取指

- Decode/Register Read

- Execute

- Memory

- Register Write

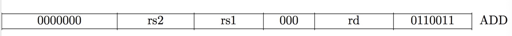

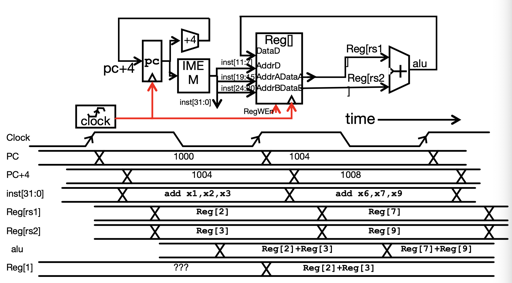

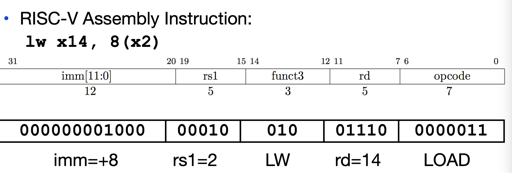

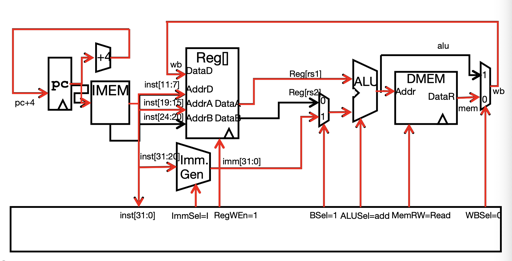

现在,我们来实现 add, 上一节我们介绍了 add ALU 对应的逻辑,现在需要看看 add 全流程了:

这个地方不涉及 memory, 需要做的事情是:

rd = rs1 + rs2PC = PC + 4

RegWEn 控制是否写寄存器,这是根据指令决定的。

- Clock edge 触发 PC 变化

- IMEM 变化,取地址

Reg[]变化,Clock 触发后输出到 ALU- 写会

rd

那么,要实现 sub, 需要给 ALU 的控制逻辑加料:

其他 R-Format Instructions 也可以用这套逻辑来实现

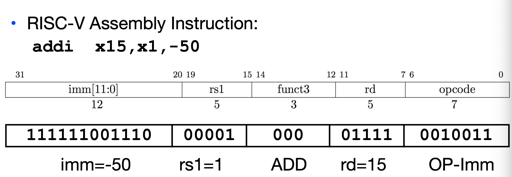

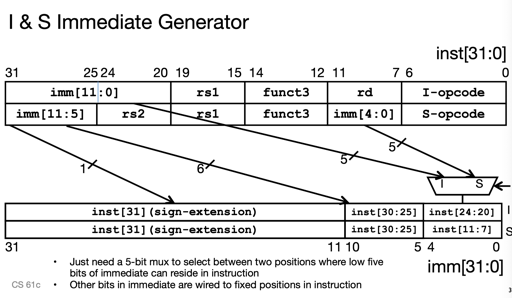

引入立即数

所以引入了 imm gen

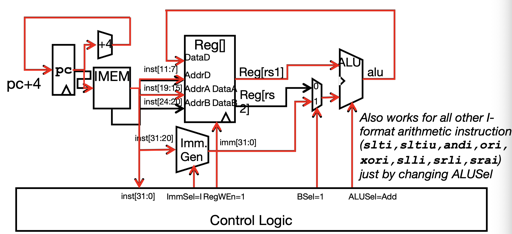

load words

现在,我们需要访问 dmem, 根据地址来输出值:

这个时候加上了 WbSel 和 MemRw, 需要读取 memory。我们现在能读取内存。

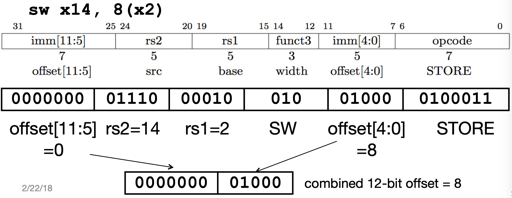

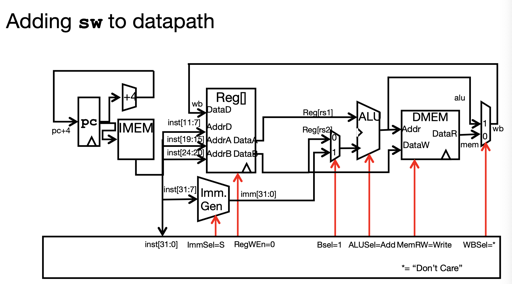

这个时候我们需要增加写内存的 Path:

这个时候需要一个 DataW 做输出到 AddR 的值。

一值多用

我们知道,RISC-V 的 rs1 rs2 rd 都是出现在同一个地方的,所以所有的路径都会被用到,只是根据控制逻辑来判断这个值具体是什么语义,是立即数还是寄存器。

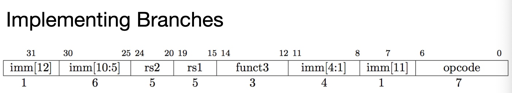

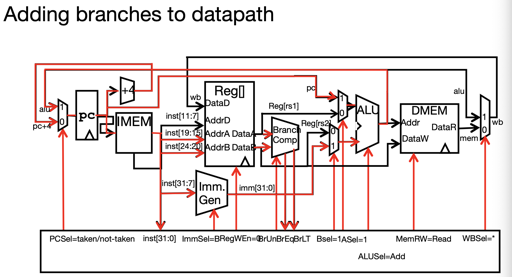

branches

Conditional branch

这里加入了一个 Branch Comp 的重要组件,然后把 PC conditional 的送到 ALU,结果再 conditional 的送回 PC

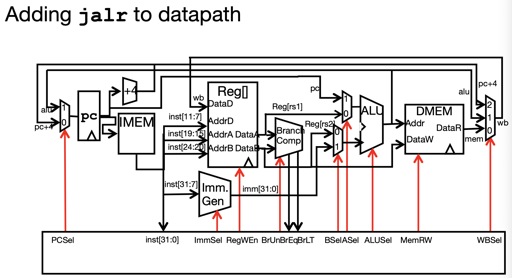

unconditional branch

这里就是直接跳转了,比之前还简单呢!

Conclusion

Universal datapath

Capable of executing all RISC-V instructions in one cycle each

Not all units (hardware) used by all instructions

5 Phases of execution

- IF, ID, EX, MEM, WB

- Not all instructions are active in all phases

- Controller specifies how to execute instructions

- what new instructions can be added with just most control?