SDS Intro & RISC-V Datapath(0): 预备知识

我们的计算机构建在电路和芯片上,虽然程序员一般不会了解这些。现在我们可能有两种电压:

Vdd, 高电压, 在树莓派里面大概是 1.2伏特- 低电压,0伏特或者接地

通常,我们选择某种中间值,大于中间值的视为 1/true, 小于这个值的设置为0/false. 高中物理实验里面我们会有个电池,然后起一个电线+物理的“switch”开关,现代我们使用 CMOS 作为这个开关:

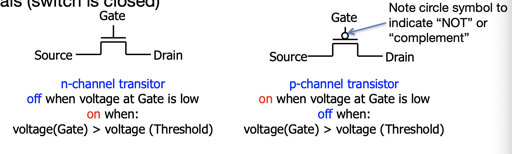

在 CMOS 中,我们实现了这种逻辑。图上的 n 是 negetive, p 是 positive, 具体如下:

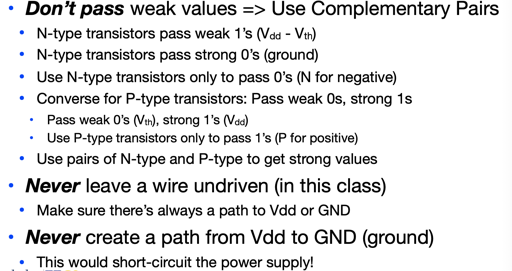

后面两条就是高中物理知识了,短路什么的…上面两条比较重要:

- n-type 不带圈,低电压时,它是通的,否则通

- p-type 带圈,高电压时,是通的,否则不通

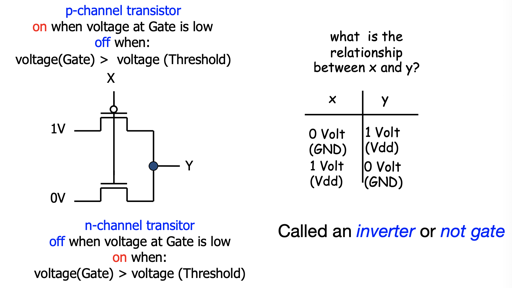

那么可以理解下面这图了:

X 为 Vdd 时,p-type 通,n-type 不通,那么 Y 电压是 1;X为 GND 时,p-type 不通,n-type 通,Y 为 0V。很显然,上面的可以算一个非门?

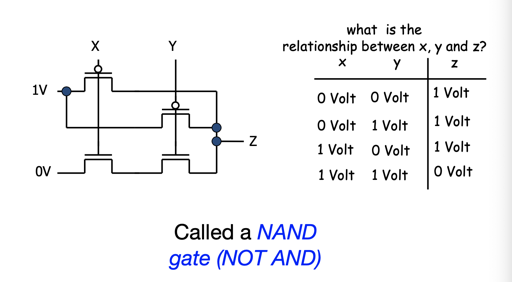

那么我们再来分析一个 slide 里的电路:

上图中,X Y 任意一个电压为一,那么 Z — 1V 中间是通的(这两个的 p-type 中并联了);而下面 n-type 串联,需要 X, Y 都为 0,它们才是通的,Z 才为 0 V。

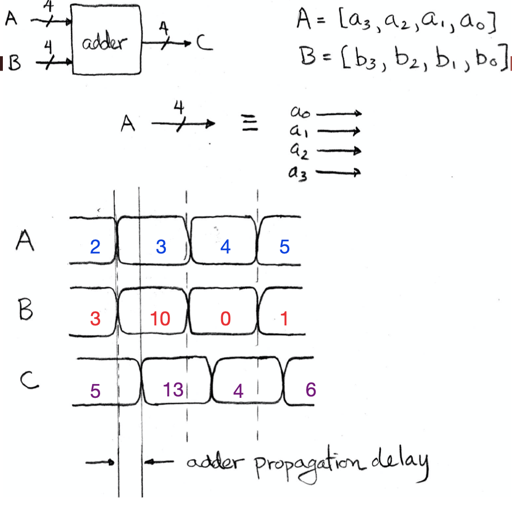

那我们可以用电路来实现一些语义,下面是你们应该都学过的一些记号,为了灌水我就贴张图了:

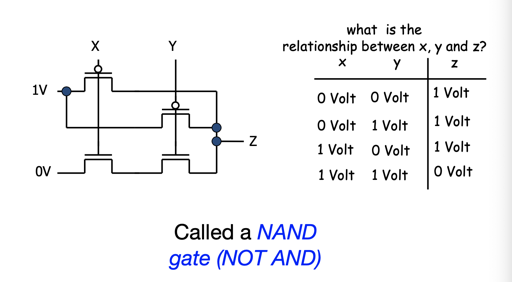

以上是相关的电路知识。实际上我们可以用几个数学工具来表示需要的逻辑:

我们可以用:

- Boolean expression: 与或非这些算子的布尔逻辑

- Truth table: 预期的输入对应的输出的所有表格

- Gate Diagram: 上述门和输入、输出的描述图

实际上,电路中是会有一些 delay 的:

反馈与触发器

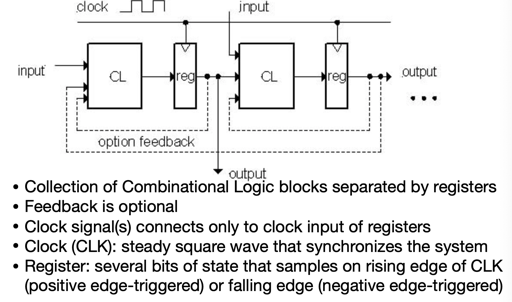

我们主要介绍 Synchronous Digital Systems,不介绍异步的系统

组合逻辑(Combinational Logic),其输出只是当前输入的函数,与之前状态无关,无存储功能;另一种是时序逻辑(Sequential Logic),能够存储数据供以后使用,如触发器,memory,寄存器(register,由多个触发器组成)。

上述内容提示我们,除了与或门和加法之类的 ALU 计算,我们还需要寄存器、内存等能够非顺时的保存状态的设备,同时,我们也需要状态,来结合上述各个部分,完成控制:比如我们有一个加法的组件,但是我们会希望让加法的结果在一定时间内是可读的,所以我们需要 flip-flop, 即触发器。

假设我们计算一个数组的和,即

1 | int sum = 0; |

我们没有地方存储 sum,那么就无法完成计算。很显然,我们需要寄存器这样的东西,那么,寄存器实际上是由一组 flip-flop 构成的.

flip-flop

Flip-flop name because the output flips and flops between 0 and 1

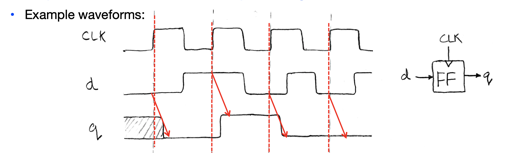

下面是 D-type flip flop, d 作为输入,q 作为输出。它是 “positive edge-triggered” 的,即变为高电压的时候,边缘触发,并保持记录。即

“On the rising edge of the clock, the input d is sampled and transferred to the output. At all other times, the input d is ignored.”

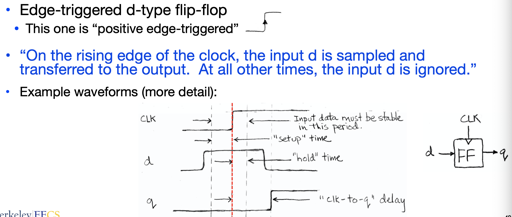

同时,高位的时间中,d 需要保持稳定,即如下图:

我们有几个关键时间,如上图:

- Setup Time: when the input must be stable before the edge of the CLK

- Hold Time: when the input must be stable after the edge of the CLK

- “CLK-to-Q” Delay: how long it takes the output to change, measured from the edge of the CLK

系统模型和时钟周期

上述是电路的基本模型,同时,对时钟周期和频率,我们有:

Period = Max Delay = CLK-to-Q Delay + CL Delay + Setup Time

Frequency = 1/Period

时间的计算会是后续的内容。

流水线

计算的每一步依赖上一步的状态,所以我们可能要多个 register, 但是不用保持过久,因为实际上我们假设模型是如上,那么每一步只依赖上一步的状态。我们可以 pipeline 的去处理指令。

回到 sum

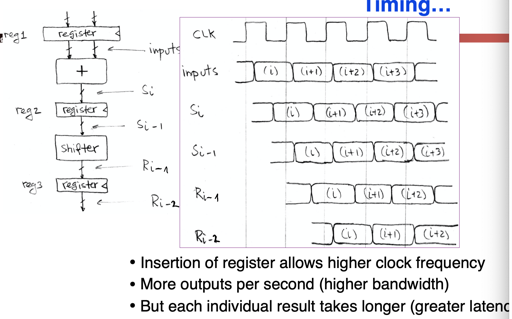

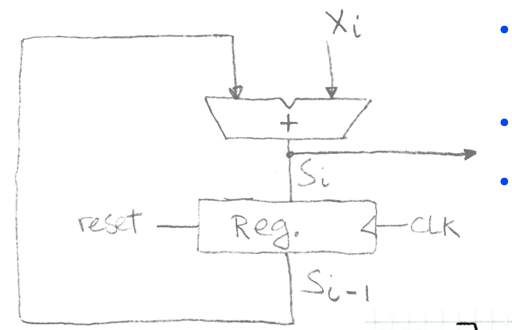

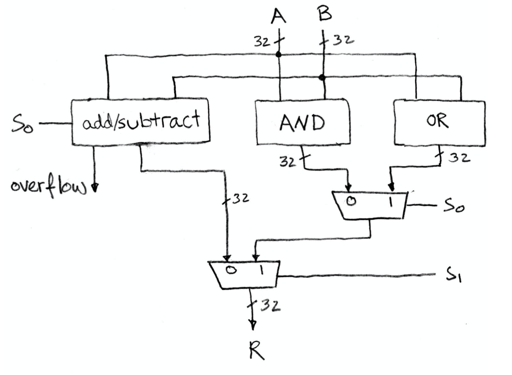

回到 sum 的计算,我们有:

S_i-1保存上一轮的 value, 由Reg持续输出S_i-1和x_i经过加法器计算出S_ireset信号将 reg 重置为 0,寄存器输出0xi开始输入x_0, 经过加法器和clk to q的时间, 提供给 Reg- CLK 起时,Reg 再次设置,成为

x0

这个时期见,period 等同于最大延迟,即 CLK-to-Q Delay + CL Delay + Setup Time

也可以观察到S_i 和 S_(i - 1) 变动的关系。

Critical path: 不能抄近道

Critical Path 指的是拿到寄存器输出的必要时间,指的是 next register 的 setup time, 也是整个逻辑电路可能的最慢的时间,即 clock 到 q 响应的时间。

极端情况是:

Clk->Q + **best case** combinational delay < Hold time

这个时候我们需要甚至人为制造一些 delay, 来让它有足够的维持时间,即 hold time,来成功输入给寄存器的 flip-flop.

逻辑设计

寄存器本身是一个状态,电路也充满了状态,我们会有上一步的状态,下一步的状态

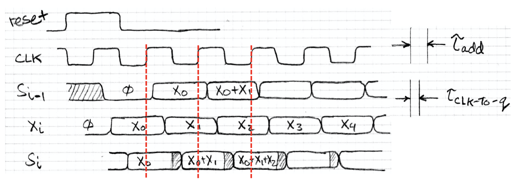

我们可以用有限状态自动机,来代表需要的逻辑。同时也可能拿到对应的输入输出的表:

Combinational logic circuit is used to implement a function that maps from present state and input to next state and output.

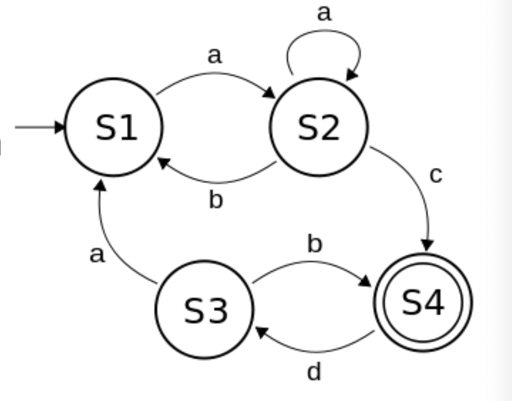

根据状态机,我们可以设计 ALU:

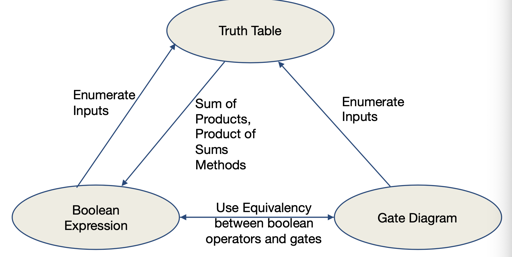

加法器

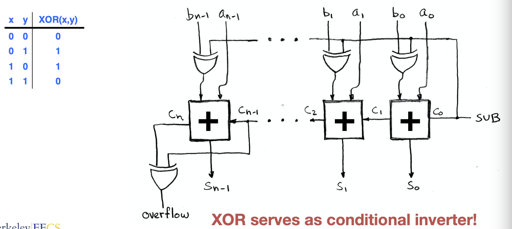

加法要有 carry-bit 实现进位,然后每两位按位相加。逻辑如下: